# Application of System-Level EM Modeling to High-Speed Digital IC Packages and PCB's

Jong-Gwan Yook, *Member, IEEE*, Linda P. B. Katehi, *Fellow, IEEE*, Karem A. Sakallah, *Senior Member, IEEE*, Ray S. Martin, Lilly Huang, and Tim A. Schreyer, *Member, IEEE*

**Abstract**—A system-level electromagnetic (EM) modeling tool combining a three-dimensional (3-D) full-wave finite-element EM-field analysis tool and a time-domain electric-circuit simulator is developed and applied to various geometries such as multilayer printed circuit boards (PCB's), signal lines embedded in a PCB or package, and split power-distribution network. Since the signal integrity is a primary concern of high-speed digital circuits, the noise distributions on various circuit planes are evaluated from the analysis. These noise distributions, often called *noise maps*, are utilized to identify the location of the major source of simultaneous switching noise (SSN). This information can eventually be adapted for optimum placement of decoupling capacitors to minimize the noise fluctuations on the various circuit planes on an entire PCB.

**Index Terms**—Circuit simulation, decoupling capacitors, EM modeling, ground bounce, PCB, SSN, tiling.

## I. INTRODUCTION

THE operating frequency of high-speed digital circuits (such as high-performance microprocessors) reaches up to gigahertz range, the switching noise (or  $\Delta I$  noise) causes serious system malfunctions. This problem continues to grow as the clock speed of circuits increases. The speed of microprocessors become almost doubled with each new microprocessor generation, yet in the personal computer (PC) market it is unacceptable to allow the design cost to increase by a similar amount. Effective and low-cost noise reduction techniques are, therefore, necessary to minimize the impact of  $\Delta I$  noise on system cost. As a result, the identification and effective suppression of the simultaneous switching noise (SSN) in the high-speed high-density digital circuits have become of critical importance.

In view of the importance of the effect of SSN, several attempts have been recently made to identify and characterize the SSN using various approximate equivalent-circuit models or experimental data [1], [2]. Further to this, with the ever increasing need for electromagnetic (EM) modeling of high-speed digital circuits and packages [3], various full-wave EM-field simulators such as the finite-element method (FEM), finite-difference time-domain (FDTD) method, and the

Manuscript received February 25, 1997; revised June 6, 1997. This work was supported under a grant from Intel Corporation.

J.-G. Yook, L. P. B. Katehi, and K. A. Sakallah are with the Department of Electrical Engineering and Computer Science, University of Michigan, Ann Arbor, MI 48109-2122 USA.

R. S. Martin, L. Huang, and T. A. Schreyer are with the Intel Corporation, Hillsboro, OR 97124-5961 USA.

Publisher Item Identifier S 0018-9480(97)07387-0.

transmission-line matrix (TLM) method are applied for more rigorous and accurate characterization of packages and high-speed digital circuits [4]–[15]. However, these full-wave tools are computationally expensive, and thus, limited to relatively simple structures.

Having realized the limitations of the equivalent circuit approaches as well as full-wave techniques on accurate and efficient modeling of digital circuits and packages, a new systematic EM-modeling methodology is proposed in this paper, and the modeling capability of the technique is proved by characterizing several practical geometries including a test vehicle. In this methodology, the seemingly contradictory goals of modeling accuracy and global analysis efficiency have been reconciled through a divide-and-conquer strategy, namely micro- and macro-modeling. The modeling accuracy is insured from the accurate full-wave EM-field simulator and the three-dimensional (3-D) FEM, and the global-analysis efficiency is achieved from the well-established time-domain circuit simulator HSPICE.

It is intended that this technique will be used to evaluate and optimize the value and placement of the decoupling capacitors for the suppression of SSN. Using this technique, the voltage distributions on the power and ground planes (noise maps) of PCB's are easily computed, and these noise maps are used to optimize the placement of decoupling capacitors as well as the pin outs of the component packages. Moreover, the driving point impedance of a whole PCB can be extracted from the voltage and current information on the noise maps. In Section II, the proposed hybrid technique is presented in detail in an effort to effectively analyze the power distribution networks of complex high-speed digital systems.

## II. SYSTEM-LEVEL EM MODELING

In view of the excessive computational requirement of 3-D full-wave EM-field simulators on one hand and modeling inaccuracy of the over simplified equivalent circuit models on the other, the characterization of high-speed digital circuits and packages requires a new systematic EM-modeling strategy. Such an approach has been presented in [16] and is summarized herein for the sake of completeness. In this approach, a given PCB or package is divided into a number of smaller rectangular units—so-called “tiles”—using a nonuniform gridding algorithm. Upon completing the gridding procedure, all of the important features of the geometry, such as via holes, signal lines, or gaps have to be captured in a way that each tile contains only one kind of discontinuity element. By following

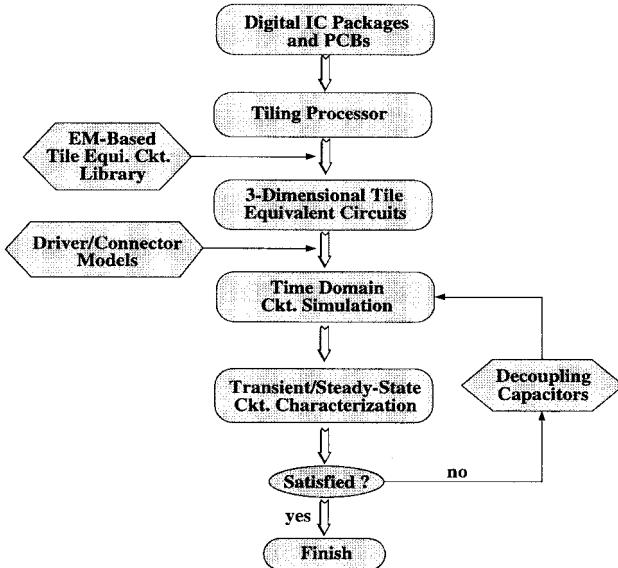

Fig. 1. System-level EM modeling of digital IC's packages and PCB's.

the above guideline, the accuracy of the modeling procedure is ensured due to the accurate tile equivalent circuits. The flexibility is also increased due to the standard shape of tiles. For example, if a given PCB has  $N$  power and ground pin's to be modeled accurately, the minimum required number of tiles becomes  $N$  so that each tile represents one power or ground pin. When a given PCB has multiple power, signal, and ground layers, the exactly same gridding procedure can be applied to generate 3-D tile-interconnection topology.

After the required set of tiles has been generated for a given PCB and a chip package, an appropriate lumped equivalent circuit model for each tile is derived from a rigorous EM-field simulation and appropriate microwave network theory. Specifically in this study, the 3D-FEM based on tetrahedral subdomain elements and linear edge basis functions is employed to derive accurate equivalent circuit models for vertical interconnection geometries. Since the PCB and the package have multiple power, ground, and signal pin's passing through different vertical layers, derivation of an accurate equivalent-circuit model of the vertical interconnects becomes a crucial step for efficient noise modeling.

While utilizing the FEM for vertical interconnects, microwave circuit theory has been applied to derive lumped equivalent circuit models for simpler structures, such as the power/ground plane, uniform signal lines, and gaps in the power distribution layers. After all the equivalent circuits corresponding to the defined tiles have been derived, these circuits are electrically interconnected to form a 3-D SPICE-type lumped equivalent circuit. Current or voltage sources are inserted into the network in addition to the connector configuration for the simulation of the actual situation.

The final stage of the proposed system-level EM modeling of high-speed digital integrated circuits (IC's) and packages is a time domain circuit simulation using a well-known SPICE-type simulator. The output of the simulation predicts potential fluctuations on the power and ground planes, noise maps, driving point impedance, and time domain noise signals on

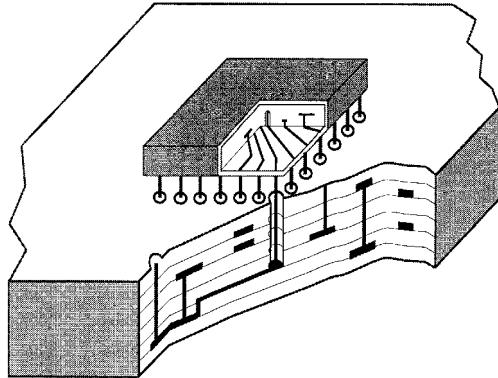

Fig. 2. Digital IC package and multilayer PCB.

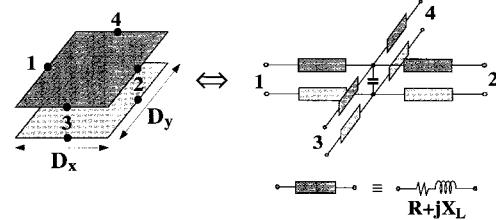

Fig. 3. Power/ground-plane tile and its equivalent circuit.

any power and ground pin's. These data provide valuable information for the efficient and cost-effective placement of decoupling capacitors to minimize the SSN in the circuits. The overall EM-modeling procedure for digital circuits and packages is illustrated in Fig. 1.

### III. TILE EQUIVALENT CIRCUITS

As mentioned above, there are several distinctive tiles forming the basic building blocks of the accurate EM-modeling procedure. Power/ground plane, power/signal/ground plane, power/ground pin, and gap in the power or ground plane are the most frequently encountered form of tiles in the high-speed digital packages and interconnects, as illustrated in Fig. 2. In this section, a brief summary of the equivalent circuits for these tiles are given [16], [17].

#### A. Power/Ground-Plane Tile

The power distribution networks of complex high-speed digital system often consist of two conducting planes—power and ground planes—connected to system reference potentials through connector. This set of planes provides a basic tile element—a so-called power/ground-plane tile—and does not include any signal lines or vertical interconnects. Using the fact that any arbitrary current flowing on the power and ground planes can be decomposed into two orthogonal components, an equivalent circuit for the tile can be derived as a four-port network, as shown in Fig. 3.

The inductive elements on the upper and lower planes represent the effects of two orthogonal current paths on the power and ground planes, while the capacitive element at the center represents the stored electric energy between the two conducting planes. Also note that resistive elements are

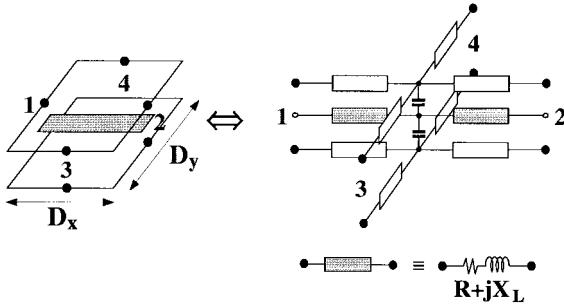

Fig. 4. Power/signal/ground-plane tile and its equivalent circuit.

inserted in series to the inductive elements to take into account the effect of conductor and dielectric losses.

The inductive and resistive elements in the lower layer corresponding to the ground plane are designed to simulate both the actual current flowing on the ground conducting surface and the resulting possible potential fluctuations. The ground plane is, therefore, no longer assumed to bear an ideal potential distribution equal to absolute zero. With this type of equivalent circuit for the power/ground-plane tile, possible SSN or  $\Delta I$  noise due to the nonideal ground plane can be fully identified.

For  $(n, m)$ th tile having dimensions  $D_x^{n, m}$  and  $D_y^{n, m}$  in the  $x$ - and  $y$ -direction, respectively, the values of the equivalent inductive, capacitive, and resistive elements are found at the given frequency  $\omega$  as follows:

$$\omega L_x^{n, m} = \frac{30\pi h}{D_y^{n, m} \sqrt{\epsilon_r}} \sin(\beta_g D_x^{n, m}) \quad (1)$$

$$\omega L_y^{n, m} = \frac{30\pi h}{D_x^{n, m} \sqrt{\epsilon_r}} \sin(\beta_g D_y^{n, m}) \quad (2)$$

$$\begin{aligned} \omega C^{n, m} = \frac{\sqrt{\epsilon_r}}{120\pi h} & \left\{ D_y^{n, m} \tan\left(\frac{\beta_g}{2} D_x^{n, m}\right) \right. \\ & \left. + D_x^{n, m} \tan\left(\frac{\beta_g}{2} D_y^{n, m}\right) \right\} \quad (3) \end{aligned}$$

$$R = \sqrt{\frac{\omega \mu_0}{2\sigma}} \quad (4)$$

where  $h$  is the distance between the planes,  $\epsilon_r$  is the dielectric constant of the material, and  $\sigma$  is the conductivity of the metal planes. These equations are valid when the electrical dimensions of the tile are much smaller than the wavelength of the operating frequency, i.e.,  $\beta_g D_{x, y}^{n, m} \ll 1$  where  $\beta_g = \omega \sqrt{\epsilon_r}/c$ ,  $c$  is the speed of light in vacuum. In most practical high-speed digital circuits, signals contain very wide-band frequency components due to their rectangular or trapezoidal shapes having very short rise and fall edges. As a result, extracting the values of the equivalent circuit at a certain frequency point may not lead to accurate noise prediction. However, if the size of a tile is much smaller than the wavelength of significant frequency component contained in the signal (as happened in most of the examples presented in this paper), the inductive and capacitive values become frequency independent.

Fig. 5. Power/ground pin tile and its equivalent circuit.

Fig. 6. Gap (slit) tile and its equivalent circuit.

### B. Power/Signal/Ground-Plane Tile

In many multilayer PCB's and packages, signal lines are embedded in the power and ground planes to achieve good isolation between the signal layers. The signal lines lying in the middle of the two conducting planes can be considered as a stripline having characteristic impedance  $Z_o$ . For a relatively narrow signal line, the current path along the signal line can be replaced with series inductance and resistive elements, while the interaction between the signal line and upper and lower conducting planes is modeled through the capacitive coupling as shown in Fig. 4.

The values of the series inductance and shunt capacitances for  $(n', m')$ th tile can be found as

$$\omega L^{n', m'} = Z_o^{n', m'} \tan\left(\frac{\beta_g}{2} D_x^{n', m'}\right) \quad (5)$$

$$\omega C^{n', m'} = \frac{1}{Z_o^{n', m'}} \sin(\beta_g D_x^{n', m'}) \quad (6)$$

where  $Z_o^{n', m'}$  is the characteristic impedance of a stripline of width  $D_y^{n', m'}$  [18]. Similar to the previous power/ground-plane tile, the above equations are valid only when the electrical size of a tile is much smaller than the wavelength of the significant frequency component contained in the signal, i.e.,  $\beta_g D_{x, y}^{n', m'} \ll 1$ .

It is important to understand how two different types of tiles are interconnected at the interface. For example, the power/ground and power/signal/ground tiles can be interfaced by connecting the node on the top layer in one tile to the node on the top layer in the other tile, while the node in the bottom layer is connected to the corresponding node in the neighboring tile. The nodes on a signal line are not connected to neighboring nodes unless there is direct current path. As a result, the overall tile equivalent circuits form 3-D lumped-element network.

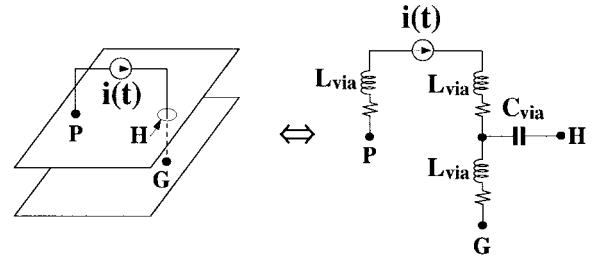

### C. Power/Ground Pin Tile

In a multilayer PCB and packaging environment, the vertical interconnect such as the power and ground pin's is one of the

Fig. 7. Split PCB. (a) Schematics of the split PCB having 14 short-circuit pin's and large void area at the center. (b) Potential distribution on top and bottom planes.

essential and most frequently encountered circuit component. Consequently, the efficient and accurate modeling of a vertical interconnect becomes a key to successful prediction of the performance of the high-speed high-density circuits. Based on physical intuition, an equivalent circuit to this structure is devised having  $LC$  elements, as shown in Fig. 5.

The inductive elements in the circuit correspond to the lead inductance, while the capacitive element represents mutual coupling between the lead and the opening in the upper plane. The values of the inductors and capacitor can be derived from the 3-D full-wave EM-field simulators, such as the 3-D FEM and FDTD method, or analytical method [19]–[26]. Particularly, in this study, the 3-D FEM is em-

ployed to discretize the vertical interconnect into a number of subdomain tetrahedral elements, and scattering parameters are calculated over a wide frequency range. The resulting  $S$ -parameters are compared with those of the equivalent circuit to determine appropriate inductance and capacitance values [15].

In general, the lead inductance is proportional to the length of the lead  $h$  and inversely proportional to the radius of the vertical lead  $r$ , i.e.,  $L_{via} \propto h$  and  $L_{via} \propto 1/r$ . When there is a via pad, the total inductance of the via structure is attributed from both the pad inductance as well as from the via itself. The capacitance due to the opening in the upper plane mainly depends on  $h$  on upper and lower sides and reveals a

Fig. 8. Eight-layer test board layout (provided by Intel Corporation).

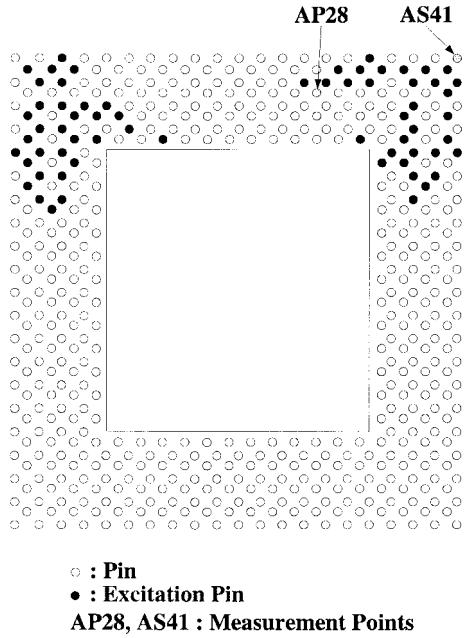

Fig. 9. Schematic of pin out and excitation pin pattern.

square-root dependency, i.e.,  $C_{\text{via}} \propto \sqrt{h}$ . Also, the coupling capacitance  $C_{\text{via}}$  sharply increases as the radius of the lead approaches that of the opening. On the contrary, as the size of the opening increases, the via capacitance decreases.

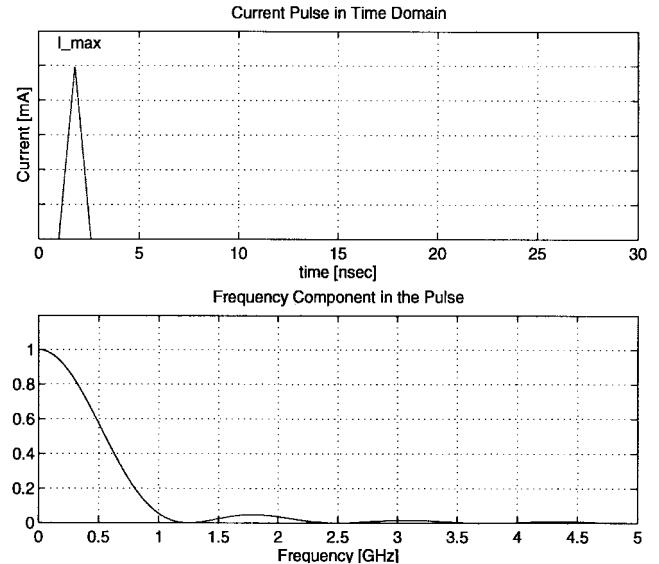

Fig. 10. Input current waveform (0.8-ns rise and fall times) and frequency components contained in the signal.

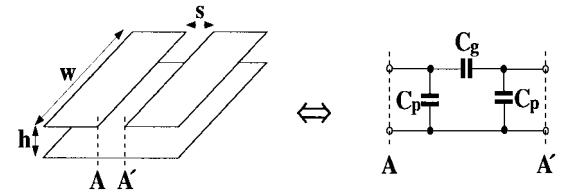

#### D. Gap (Slit) Tile

In many multilayer PCB structures, conducting planes are split into two or more regions to reduce overall switching noise. For the modeling of the effect of gaps in split planes, capacitive elements which correspond to the parasitic electric

Fig. 11. Relative potential fluctuations between the power and ground planes.

energy stored in the gap region are employed, as shown in Fig. 6. Due to the discontinuity of the structure, there are no conducting currents flowing across the gap allowing the capacitive effect to be a dominant one. The gap tile is implemented by removing inductive elements from the power/ground-plane tile and instead inserting the capacitors corresponding to gap and parasitic electric fields.

Accurate values or equations of the gap and parasitic capacitances  $C_g$  and  $C_p$  can be determined from the equivalent circuit of a microstrip gap discontinuity geometry found in [27]–[31]. In this study, the following equations are derived from functional approximations and are employed by [31] for a symmetrical structure:

$$C_g = \frac{h}{2} Q_1 e^{-1.86(s/h)} \left\{ 1 + 4.19(1 - e^{-0.785\sqrt{h/w}}) \right\} \quad (7)$$

$$C_p = C_L \frac{Q_2 + (e^{-0.5978} - 0.55)}{1 + Q_2} \quad (8)$$

where

$$Q_1 = 0.04598 \left\{ 0.03 + \left( \frac{w}{h} \right)^{1.23} \right\} (0.272 + 0.07\epsilon_r)$$

$$Q_2 = 0.107 \left[ \frac{w_2}{h} \right] + 9 \left( \frac{s}{h} \right)^{3.23} + 2.09 \left( \frac{s}{h} \right)^{1.05} \left( \frac{1.5 + 0.3w/h}{1 + 0.6w/h} \right).$$

The equation of the terminal capacitance  $C_L$  for an open circuit with conductor width  $w$  can be found in [32]. The normalized terminal capacitance  $C_L/w$  reduces with decreasing  $w/h$  and approaches a value of  $C_{L,\infty}/w \simeq 0.012 + 0.0039\epsilon_r$  in

picofarad/millimeter for large conductor width  $w/h \geq 1$ . In (7) and (8),  $C_g$  is in picofarad and  $h$  in millimeter. The above equations are valid for the ranges  $0.1 \leq w/h \leq 3.0$  and  $0.2 \leq s/h \leq \infty$ , for substrate permittivities  $6.0 \leq \epsilon_r \leq 13$ , and in the frequency range  $0 \leq h \cdot f \leq 12 \text{ GHz} \cdot \text{mm}$ . For a substrate having  $\epsilon_r$  outside of the valid region, the capacitances can be estimated with  $C(\epsilon_r) = C(9.6) \cdot (\epsilon_r/9.6)^{0.9}$ . In our modeling procedure, the above constraints are carefully enforced during the tiling procedure unless otherwise specified.

It can be seen that  $C_g$  and  $C_p$  approximately increase linearly with  $\epsilon_r$  for constant  $w/h$  and  $s/h$ . Note that for large values of  $s/h$ ,  $C_g$  approaches to zero, corresponding to an open circuit. On the other hand, as  $s/h$  approaches to zero, the value of the parasitic capacitances  $C_p$  becomes smaller. When the gap spacing  $s$  becomes much larger than the tile-width  $w$ , the gap tile is modeled as an open circuit having only parasitic capacitance  $C_p$ .

#### IV. NUMERICAL RESULTS

In this section, by using the proposed system-level EM-modeling technique, several interesting and practical geometries are modeled to characterize SSN on multilayer PCB and packaging environment. Firstly, the effect of splitting the top plane into two regions is modeled, and resulting potential fluctuations on top and bottom planes are computed. Secondly, a test vehicle having eight layers of power, signal, and ground planes is fully modeled and compared with the voltage measurement on various places. The effects of signal lines embedded between the power and ground planes are also closely examined with an actual buffer model.

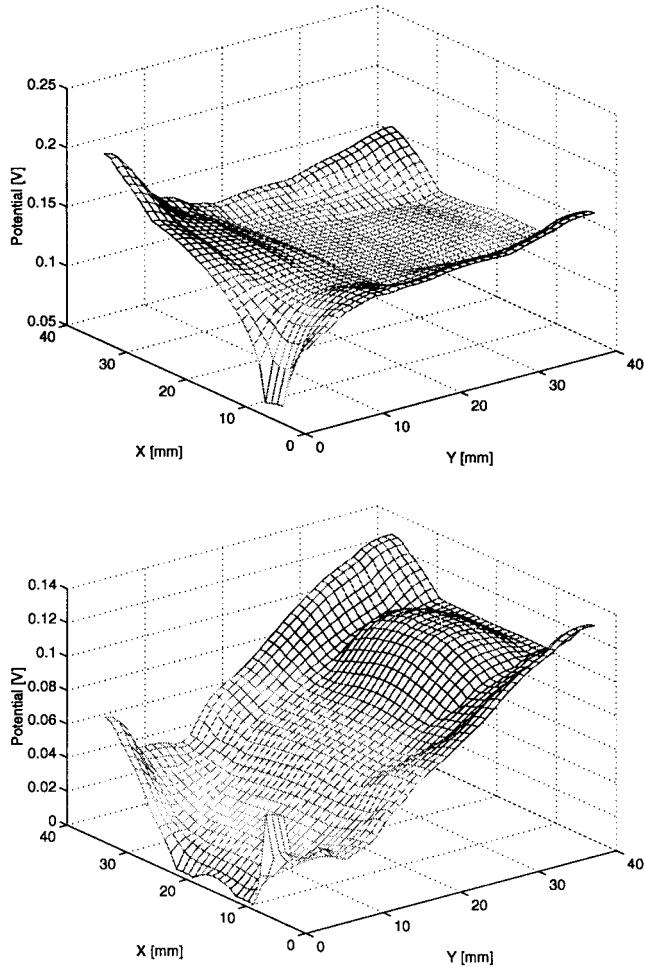

Fig. 12. Noise maps (peak-to-peak potential fluctuations) on the power and ground planes.

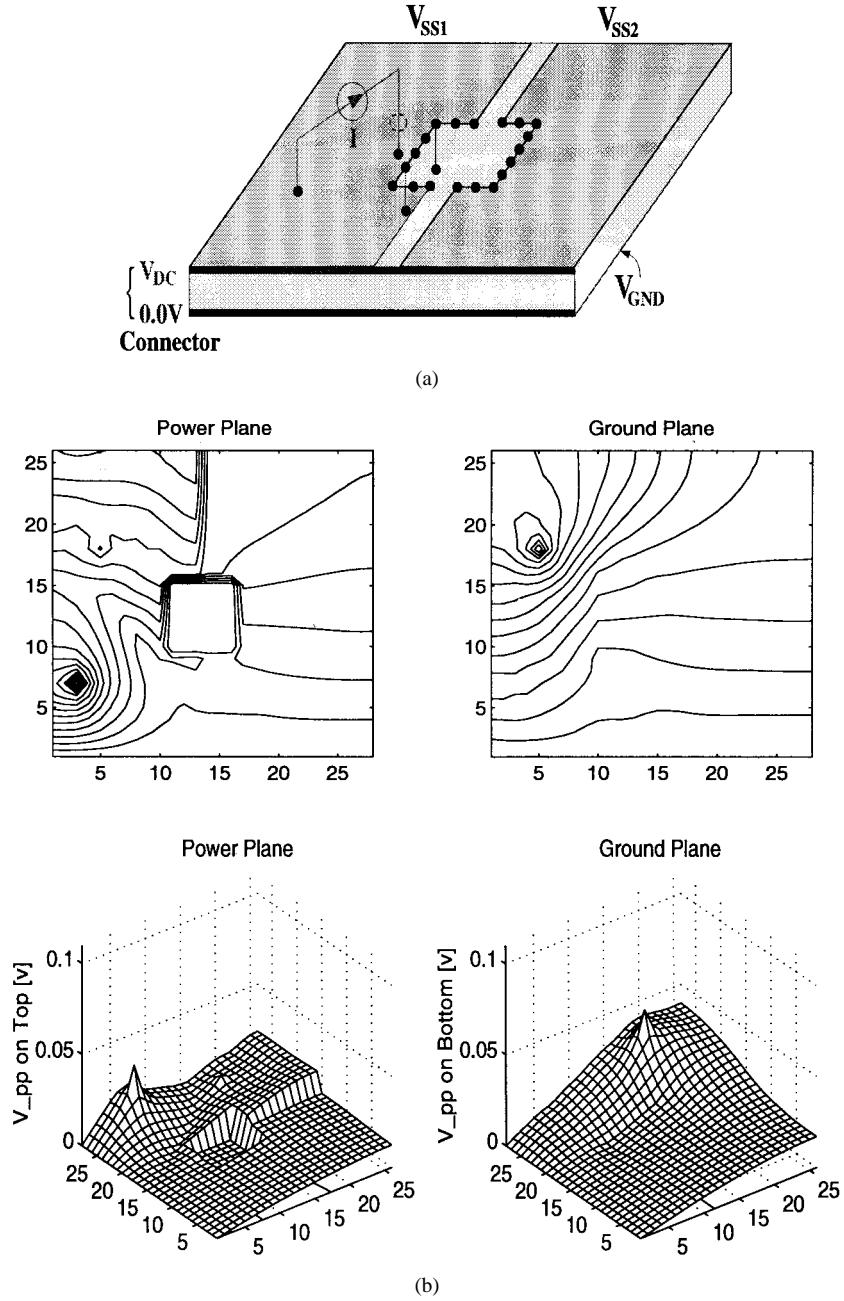

#### A. Split PCB

In this section, a 64 mm  $\times$  64 mm PCB is modeled with 26  $\times$  28 nonuniform tiles. As shown in Fig. 7(a), the upper plane is split into two regions. The gap spacing and the thickness of the substrate are 2.54 and 0.2 mm, respectively, and the relative dielectric constant  $\epsilon_r$  of the material is 2.5. 14 short-circuit pin's modeled as inductive elements are also placed at the central region to reduce the overall noise levels on top and bottom planes. For the excitation of the structure, one current source is supplied as shown in Fig. 7(a) and the input current waveform is designed to have 100-mA magnitude and 0.5-ns rise and fall time. In view of high-frequency components contained in the signal, the equivalent circuits are extracted at  $f = 2$  GHz. Also, a connector providing 2.5 and 0.0 V on the top and bottom planes is placed at the front side of the PC board.

After the EM modeling of the overall geometry, an efficient circuit simulation is exercised to derive the potential distribution on the top and bottom planes. After 10 ns of time-domain simulation, the peak-to-peak values at each grid point on the top and bottom planes and the corresponding noise maps are derived, as shown in Fig. 7(b). The maximum noise on those

Fig. 13. Cross-sectional view of a signal line terminated with capacitive load. Top and bottom planes: 175 mm  $\times$  184 mm. Length of the signal line = 5.0 mm.  $C_{load} = 18$  pF,  $R_{dd} = R_{gnd} = R_{out} = 0.001$   $\Omega$ .

Fig. 14. Simulated current waveforms at the output resistor ( $R_{out}$ ) and capacitive load ( $C_{load}$ ).

planes are 47.7 and 66.7 mV, respectively, at the position of the current source. As can be observed, there is clearly a potential difference between the top two planes due to the 2.54-mm gap region revealing effective noise immunization of splitting PCB's.

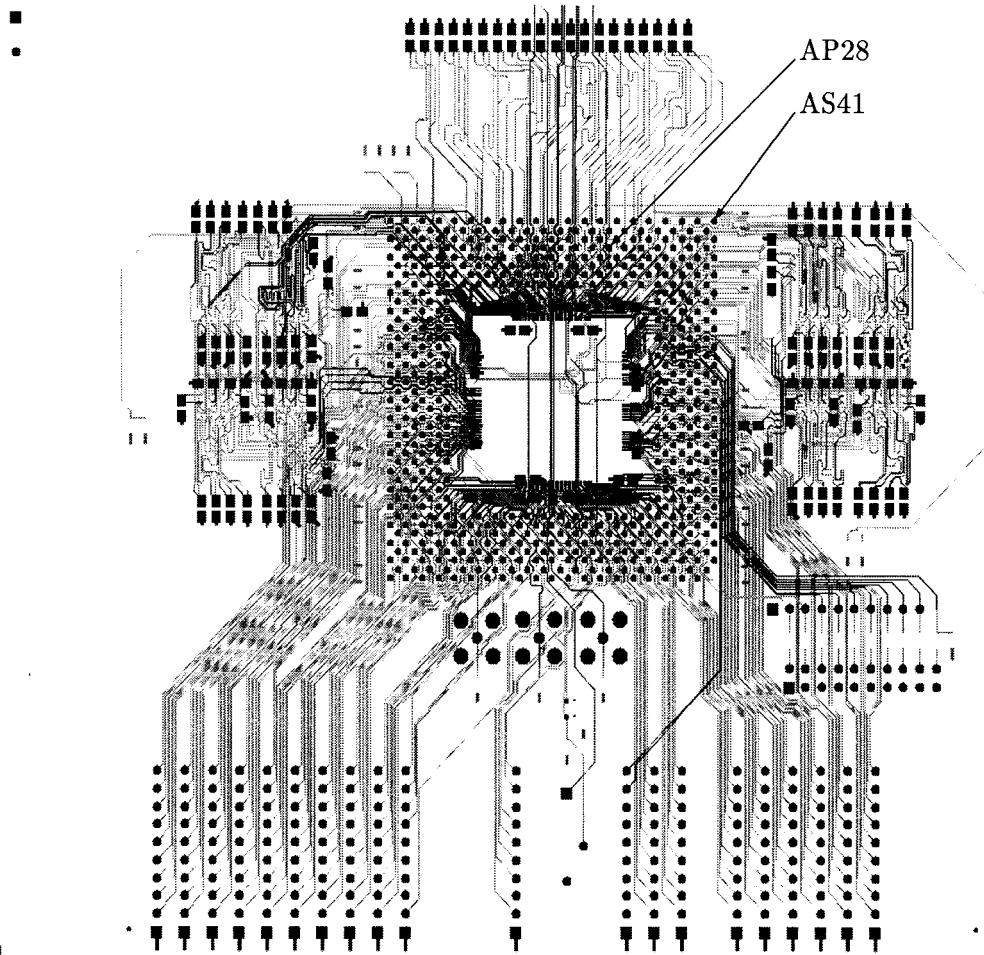

#### B. Eight-Layer Test Board

For the proof of the accuracy as well as efficiency of the proposed approach, an eight-layer test vehicle, shown partly in Fig. 8, is fully modeled and the noise level is measured under a controlled environment. To minimize the measurement errors and uncertainties, multiple CMOS drivers are simultaneously switched, as shown in Fig. 9, and the voltage differences between the power and ground planes at various locations are measured and compared with the modeled results. For accurate and efficient modeling, the test PCB is discretized into a number of tiles (34  $\times$  37 nonuniform tiles) and 64 ideal triangular current sources are simultaneously excited between the power and ground pin's at various places. Those 64 sets of power and ground pin's form two groups (32 in each group) and each aggregated current source group is located in the upper left and right corner of the chip area, as shown in Fig. 9. For simulation purposes, ideal current sources having 0.8-ns rising and falling times are used and its frequency

Fig. 15. Simulated potential fluctuations on the power (node 1147) and ground plane (node 2433) with a signal line terminated with capacitive load. The voltage difference between the power and ground plane is denoted as  $\Delta V$ , which is indicating a noisy power-distribution layer.

content are shown in Fig. 10. The triangular shape of the input currents with 15-mA magnitude is estimated from the actual CMOS driver. Note that the Fourier components in the input current signal span up to near gigahertz range due to the fast edge rates.

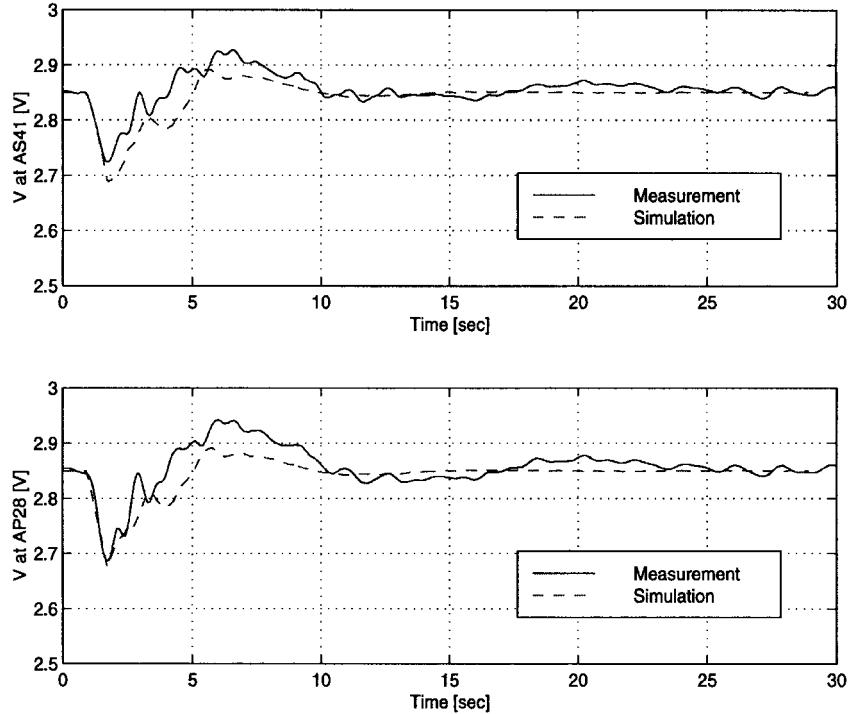

As shown in Fig. 11, simulation has been performed and the voltage waveforms at two different locations denoted as *AS41* and *AP28* are compared with the measurement data. These measurement points are located in the upper right corner of the chip area. The overall simulation, including tiling procedure and circuit simulation, took about 3 h on an HP 9000/735 workstation with 130-Mbytes memory usage. As can be observed from the voltage waveforms, the measurement and simulation results reveal very good agreement even for the small details. This agreement supports the validity and effectiveness of the proposed system-level EM-modeling technique. In addition, noise maps (peak-to-peak values) on the power and ground planes are illustrated in Fig. 12 and the maximum values on the power- and ground-plane noise maps are found as  $V_{pp}^{pwr} = 205$  mV and  $V_{pp}^{gnd} = 134$  mV, respectively. Note that the minima in the noise maps correspond to the connector locations which provide constant potentials.

### C. Signal Lines

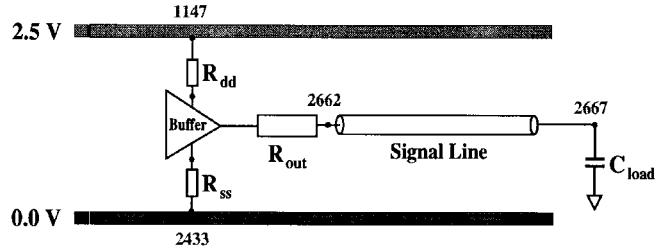

After the verification of the accuracy of the proposed modeling procedure, in this section the effects of nonlinear drivers and signal lines terminated with capacitive loads are simulated, using the power/signal/ground-plane geometry designed with

one signal line, as depicted in Fig. 13. The geometrical factors of the PCB are similar to those of the previous test vehicle and the signal line is placed in the middle of the substrate. The buffer model used in this study has three terminals, such as  $V_{dd}$ ,  $V_{gnd}$  and output, and those are connected to  $0.001 \Omega$  resistors,  $R_{dd}$ ,  $R_{gnd}$ , and  $R_{out}$ , respectively, while an input excitation having 0.4-ns switching time is embedded in the driver model. In the buffer model, p- and n-channel CMOS look-up tables are used to simulate the actual transistor characteristics.

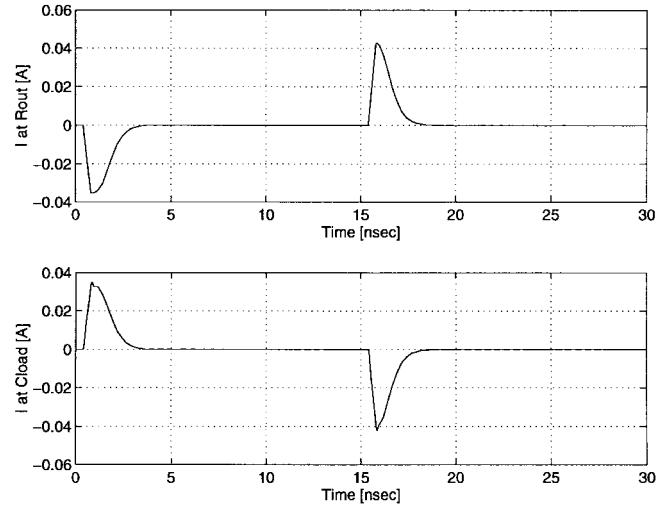

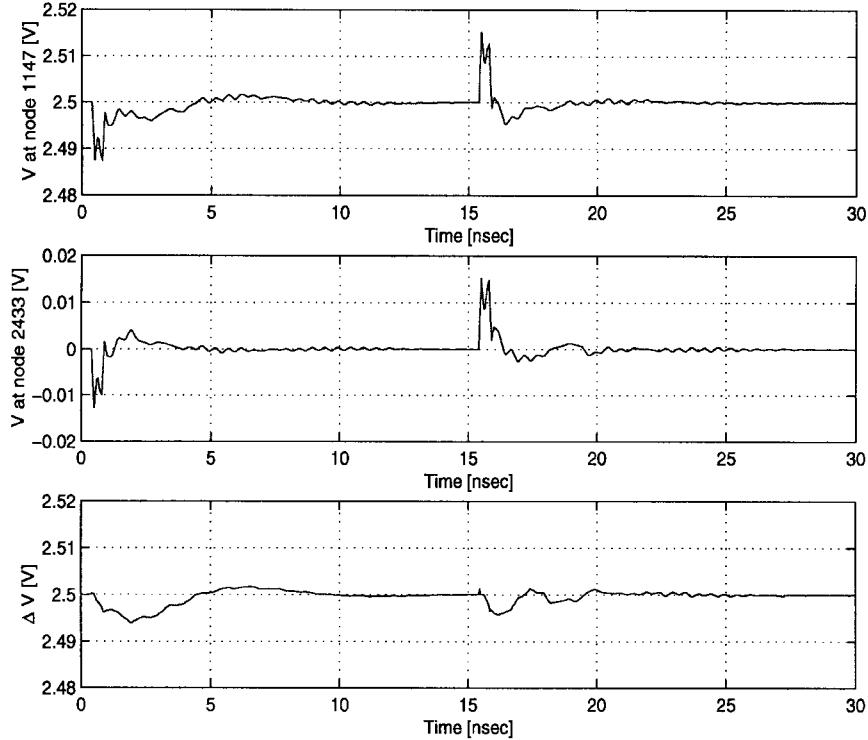

After 30-ns transient analysis, the current waveforms at the output resistor  $R_{out}$  and capacitive load  $C_{load}$  are examined first, as illustrated in Fig. 14. As can be identified from the current waveforms, there is a slight reflection at the beginning of the signal line due to the impedance mismatch and the phase of current at the capacitor is reversed. Also, Fig. 15 shows the voltage waveforms on the power and ground planes revealing ground bounce caused from a nonideal ground plane. The potential difference between the power and ground planes can be considered as noise if that is not constant and equal to the connector potential, which in this case is 2.5 V.

## V. CONCLUSIONS

This paper has presented a system-level methodology for the modeling and analysis of digital IC packages and PC boards. In this methodology, the seemingly contradictory goals of modeling accuracy and global analysis efficiency are reconciled through a divide-and-conquer process. Accuracy is insured by performing detailed EM-field analysis on appropriately

chosen small sections of the PCB and package to create lumped electrical equivalent circuit models. These models are subsequently combined with models for chip current drivers and package leads to produce an electrical simulation model for the PCB power distribution subsystem. A circuit simulator is then used to exercise this model under a variety of current excitation conditions to yield noise maps that indicate the variation in power and ground potential as a function of location on the PCB.

The validity and efficiency of our proposed system-level EM-modeling methodology have been proven through several different experiments including a split PCB and an eight-layer test vehicle. The theoretical results for the test board show very good agreement with the measurement data obtained from the actual board under control environment. Owing to the flexibility of the modeling method, voltage and current waveforms at arbitrary locations can easily be made visible. Furthermore, the effects of signal lines, gap in the conducting plane, and decoupling capacitances can be quantified.

#### ACKNOWLEDGMENT

The authors would like to express their thanks to Dr. T. Arabi of Intel Corporation, Hillsboro, OR, for many helpful discussions.

#### REFERENCES

- [1] B. A. Ziegner, "High performance MMIC hermetic packaging," *Microwave J.*, pp. 133-139, Nov. 1986.

- [2] H. Bierman, "Designers strive for low cost MMIC packages," *Microwave J.*, pp. 100-106, Sept. 1992.

- [3] L. P. B. Katehi, "The role of EM modeling in integrated packaging," in *1993 IEEE AP-S Dig.*, Ann Arbor, MI, July 1993, pp. 982-985.

- [4] J. Fang, "Electromagnetic modeling of electronics packaging by the time-domain finite-difference methods," in *IEEE Topical Meeting Elect. Performance Electron. Packaging*, Tucson, AZ, Apr. 1992, pp. 90-92.

- [5] S. Zaage, D. Kannemacher, and H. Grabinski, "Characterization of the electrical performance of PGA packages," in *IEEE Topical Meeting Elect. Performance Electron. Packaging*, Tucson, AZ, Apr. 1992, pp. 134-136.

- [6] L. X. Lu, C. Wu, and J. Litva, "A new three-dimensional finite-difference time-domain (3D-FDTD) simulator for modeling electronic interconnections and packaging," in *IEEE Topical Meeting Elect. Performance Electron. Packaging*, Monterey, CA, Oct. 1993, pp. 92-95.

- [7] J. Fang, Y. Liu, Y. Chen, Z. Wu, and A. Agrawal, "Modeling of power/ground plane noise in high speed digital electronics packaging," in *IEEE Topical Meeting Elect. Performance Electron. Packaging*, Monterey, CA, Oct. 1993, pp. 206-208.

- [8] Y. Chen, Z. Chen, Z. Wu, D. Xue, and F. Fang, "A new approach to signal integrity analysis of high-speed packaging," in *IEEE Topical Meeting Elect. Performance Electron. Packaging*, Portland, OR, Oct. 1995, pp. 236-238.

- [9] F. Y. Yuan, "Signal integrity analysis of simultaneous switching noises and decoupling capacitors in digital packages and PCB systems," in *IEEE Topical Meeting Elect. Performance Electron. Packaging*, Napa, CA, Oct. 1996, pp. 132-134.

- [10] Y. Chen, R. Mittra, P. Harms, and W. Beyene, "A technique for deriving the equivalent circuit of an SOP package using the FDTD in conjunction with TOUCHSTONE," in *IEEE Topical Meeting Elect. Performance Electron. Packaging*, Napa, CA, Oct. 1996, pp. 135-137.

- [11] M. Falconer and V. Tripathi, "FDTD simulation of power/ground bounce and crosstalk in IC packages," in *IEEE Topical Meeting Elect. Performance Electron. Packaging*, Napa, CA, Oct. 1996, pp. 166-168.

- [12] W. J. R. Hoefer, "Time domain modeling of high-speed circuit structures with TLM," in *IEEE Topical Meeting Elect. Performance Electron. Packaging*, Napa, CA, Oct. 1996, pp. 196-198.

- [13] J.-G. Yook, N. Dib, E. Yasan, and L. Katehi, "A study of hermetic transitions for microwave packages," in *1995 IEEE MTT-S Int. Microwave Symp. Dig.*, Orlando, FL, May 1995, pp. 1579-1582.

- [14] M. Rittweger, M. Werthen, J. Kunisch, I. Wolff, P. Chall, B. Balm, and P. Lok, "3-D FDTD analysis of a SOT353 package containing a bipolar wide-band cascode transistor using compression approach," in *1995 IEEE MTT-S Int. Microwave Symp. Dig.*, Orlando, FL, May 1995, pp. 1587-1590.

- [15] J.-G. Yook, N. Dib and L. Katehi, "Characterization of high frequency interconnects using finite difference time domain and finite element methods," *IEEE Trans. Microwave Theory Tech.*, vol. 42, pp. 1727-1736, Sept. 1994.

- [16] J.-G. Yook, V. Chandramouli, L. Katehi, K. Sakallah, T. Arabi, and T. Schreyer, "Computation of switching noise in printed circuit boards," *IEEE Trans. Comp., Packag., Manufact. Technol. A*, vol. 20, Mar. 1997.

- [17] J.-G. Yook, T. Arabi, T. Schreyer, L. Katehi, and K. Sakallah, "System level EM modeling of digital IC packages and PC boards," presented at the *IEEE Topical Meeting Elect. Performance Electron. Packaging*, Napa, CA, Oct. 1996.

- [18] H. H. Howe, *Stripline Circuit Design*. Norwood, MA: Artech House, 1974.

- [19] T. Wang, R. Harrington, and J. Mautz, "The equivalent circuit of a via," *Trans. Soc. Comput. Simulations*, vol. 4, pp. 97-123, Apr. 1987.

- [20] T. Wang, R. Harrington, and J. Mautz, "Quasi-static analysis of a microstrip via through a hole in a ground plane," *IEEE Trans. Microwave Theory Tech.*, vol. 36, pp. 1008-1013, June 1988.

- [21] M. Goldfarb and R. Pucel, "Modeling via hole grounds in microstrip," *IEEE Microwave Guided Wave Lett.*, vol. 1, pp. 135-137, June 1991.

- [22] P. A. Kok and D. De Zutter, "Capacitance of a circular symmetry model of a via hole including finite ground plane thickness," *IEEE Trans. Microwave Theory Tech.*, vol. 39, pp. 1229-1234, July 1991.

- [23] P. A. Kok and D. De Zutter, "Scalar magnetostatic potential approach to the prediction of the excess inductance of grounded via's and via's through a hole in a ground plane," *IEEE Trans. Microwave Theory Tech.*, vol. 42, pp. 1229-1237, July 1994.

- [24] J. Quine, H. Webster, H. Glascock, and R. Carlson, "Characterization of via connections in silicon circuit boards," *IEEE Trans. Microwave Theory Tech.*, vol. 36, pp. 21-27, Jan. 1988.

- [25] D. Swanson, "Grounding microstrip lines with via holes," *IEEE Trans. Microwave Theory Tech.*, vol. 40, pp. 1719-1721, Aug. 1992.

- [26] Q. Gu, E. Yang, and M. Tassoudji, "Modeling and analysis of vias in multilayered integrated circuits," *IEEE Trans. Microwave Theory Tech.*, vol. 41, pp. 206-214, Feb. 1993.

- [27] P. Benedek and P. Silvester, "Equivalent capacitances for microstrip gaps and steps," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-20, pp. 729-733, Nov. 1972.

- [28] R. Garg and I. J. Bahl, "Microstrip discontinuities," *Int. J. Electron.*, vol. 45, no. 1, pp. 81-87, 1978.

- [29] A. Gopinath and C. Gupta, "Capacitance parameters of discontinuities in microstriplines," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-26, pp. 831-836, Oct. 1978.

- [30] R. K. Hoffmann, *Handbook of Microwave Integrated Circuits*. Norwood, MA: Artech House, 1987.

- [31] M. Kirschning, R. H. Jansen, and N. H. L. Koster, "Measurement and computer-aided modeling of microstrip discontinuities by an improved resonator method," in *IEEE MTT-S Int. Symp. Dig.*, Boston, MA, 1983, pp. 495-497.

- [32] ———, "Accurate model for open end effect of microstrip lines," *Electron. Lett.*, vol. 17, no. 3, pp. 123-124, 1981.

**Jong-Gwan Yook** (S'86-M'97) was born in Korea, in 1964. He received the B.S. and the M.S. degree in electronic engineering from Yonsei University, Seoul, Korea, in 1987 and 1989, respectively, and the Ph.D. degree from the University of Michigan at Ann Arbor, in 1996.

He is currently working in the Radiation Laboratory, University of Michigan at Ann Arbor, as a Research Fellow. His main research interests are in the area of EM design and characterization of microwave/millimeter-wave circuits and components and VLSI and MMIC interconnects using the FEM, and development of numerical techniques for analysis and design of high-speed high-frequency circuits with emphasis on parallel/super computing.

**Linda P. B. Katehi** (S'81–M'84–SM'89–F'95) received the B.S.E.E. degree from the National Technical University of Athens, Athens, Greece, in 1977, and the M.S.E.E. and Ph.D. degrees from the University of California at Los Angeles, in 1981 and 1984, respectively.

In 1984, she joined the faculty of the EECS Department, University of Michigan at Ann Arbor. Since then, she has been interested in the development and characterization (theoretical and experimental) of microwave, millimeter-

printed circuits, the computer-aided design of VLSI interconnects, the development and characterization of micromachined circuits for millimeter-

wave and submillimeter-wave applications, and the development of low-loss

lines for Terahertz-frequency applications. She has also been theoretically

and experimentally studying various types of uniplanar radiating structures

for hybrid-monolithic and monolithic oscillator and mixer designs.

Dr. Katehi is a member of the IEEE Antennas and Propagation Society, Microwave Theory and Techniques Society, Sigma XI, Hybrid Microelectronics, URSI Commission D, and a member of IEEE Antennas and Propagation Society ADCOM from 1992 to 1995. She also serves as an associate editor for the IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES. She has been awarded the IEEE Antennas and Propagation Society W. P. King (Best Paper Award for a Young Engineer) in 1984, the IEEE Antennas and Propagation Society S. A. Schelkunoff Award (Best Paper Award) in 1985, the NSF Presidential Young Investigator Award, and an URSI Young Scientist Fellowship in 1987, the Humboldt Research Award and the University of Michigan Faculty Recognition Award in 1994, and the IEEE Microwave Theory and Techniques Society Microwave Prize in 1996.

**Ray S. Martin** received the A.S. degree from Mount Hood Community College, Gresham, OR, in 1978.

He is currently a Hardware Design Engineer at Intel Corporation, Hillsboro, OR, where he specializes in the design of printed circuit-board interconnections and the development of tools that assist in the design of interconnects.

**Lilly Huang** was born in Beijing, China. She received the Ph.D. degree in electrical engineering from the University of Wisconsin, Milwaukee, in 1995.

She is currently a Senior Engineer at Intel Corporation, Hillsboro, OR, where she specializes in system power distribution and processor power delivery, and development of new techniques for designing power-distribution architecture. Her research interests include the development and characterization of processor power-delivery systems, high-speed interconnects, MMIC packaging, and EM modeling.

**Karem A. Sakallah** (S'78–M'80–SM'92) received the B.E. degree with distinction in electrical engineering from the American University of Beirut, Beirut, Lebanon, in 1975, and the M.S.E.E. and Ph.D. degrees in electrical and computer engineering from Carnegie–Mellon University (CMU), Pittsburgh, PA, in 1977 and 1981, respectively.

In 1981, he joined the Department of Electrical Engineering, CMU, as a Visiting Assistant Professor. From 1982 to 1988, he was with the Semiconductor Engineering Computer-Aided Design Group, Digital Equipment Corporation, Hudson, MA, where he headed the analysis and simulation advanced development team. Since September 1988, he has been at the University of Michigan at Ann Arbor, as Professor of electrical engineering and computer science. From 1994 to 1995, he was on a six-month sabbatical leave at the Cadence Berkeley Laboratory, Berkeley, CA. His research interests are primarily in the area of computer-aided design, with particular emphasis on numerical analysis, multilevel simulation, timing verification and optical clocking, modeling, knowledge abstraction, and design environments.

Dr. Sakallah is a member of the ACM and Sigma Xi. He is an associate editor for the IEEE TRANSACTIONS ON COMPUTER-AIDED DESIGN OF INTEGRATED CIRCUITS AND SYSTEMS.

**Tim A. Schreyer** (S'82–M'83) received the Ph.D. degree from Stanford University, Stanford, CA, in 1989.

He is currently a Senior Staff Engineer at Intel Corporation, Hillsboro, OR, where he specializes in signal integrity and transmission-line modeling of printed circuit-board interconnections, and the development of new techniques for designing high-speed interconnections, and teaching these techniques to other system designers.